p n是什么_p n是什么意思

*** 次数:1999998 已用完,请联系开发者***

英迪迈取得高效节能型P+N沟道驱动电路专利,实现高效节能金融界2024年3月20日消息,据国家知识产权局公告,英迪迈智能驱动技术无锡股份有限公司取得一项名为“一种高效节能型P+N沟道驱动电路“,授权公告号CN107959491B,申请日期为2017年12月。专利摘要显示,本发明公开一种高效节能型P+N沟道驱动电路,包括上桥电路和下桥电路;...

扬杰科技申请一种多导电沟道的平面栅 MOSFET 及制备方法专利,降低...在器件的的 P 体区和 P+沟道区之间形成一个薄的 N+层,关态状态下 G 极电极不加电压,该 N+层在 P 体区和 P+沟道区的夹持下被完全耗尽,不导电,开态状态下 G 极电极加正电压,栅氧一侧 P+沟道区形成反型层导电沟道,同时由于 G 极电极加正电压,P 体区和 P+沟道区夹持的 N+层由完全...

(^人^) 一道新能申请一项 IBC 电池及其制备方法专利,解决现有 IBC 电池金属...方法包括:在硅片背面形成相互间隔的 P+发射极和 N+发射极后,在 P+发射极和 N+发射极表面形成介质层;在所述介质层上方放置转印衬底,所述转印衬底中包括金属浆料;将所述转印衬底中的金属通过激光转印至所述介质层中,以形成与所述 P+发射极接触的正电极种子层、以及与所述 N+...

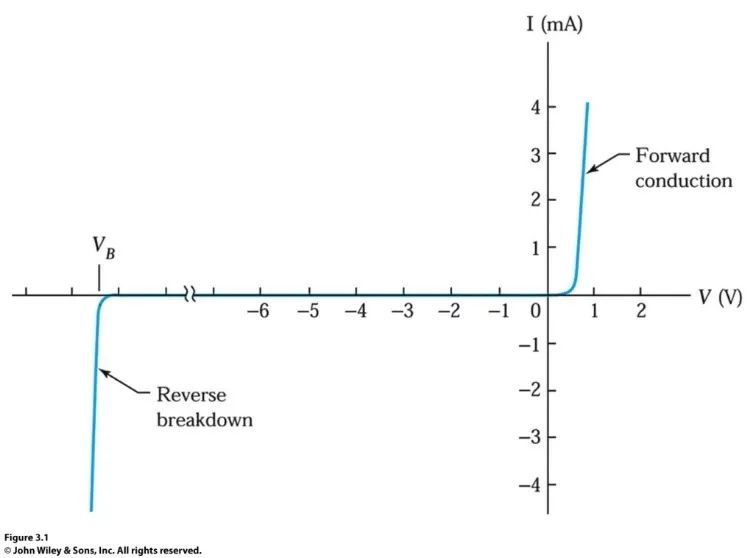

比亚迪申请晶体管和用电设备专利,提高晶体管的耐压稳定性金融界2024年9月3日消息,天眼查知识产权信息显示,比亚迪股份有限公司申请一项名为“晶体管和用电设备“,公开号CN202410683547.X,申请日期为2024年5月。专利摘要显示,一种晶体管和用电设备,晶体管包括P+型屏蔽层、肖特基电极、N型接触区;其中,P+型屏蔽层包括第一面;肖特...

北京亦庄加快建设数据基础制度先行区 推进2000P算力中心建设人民网北京2月1日电 (记者池梦蕊)2月1日,记者从北京市政府新闻办公室举行的新闻发布会上获悉,北京亦庄(北京经济技术开发区)正加快建设2000P(1P约等于每秒1000万亿次的计算速度)规模公共智能算力中心,构建“1+3+N”体系,推进数据基础制度先行区建设。北京经济技术开发区工...

养狗一年真心回购n多次的零食推荐n p y都嫉妒狗子吃那么好!这个大小当非常适合中大型犬的training treat而且是high value treat 海鲜味十足 口水哇啦啦的3. Plato pet treats的... 俩一块真的太大了而且不容易掰开刚吃完的两包主要是用来睡前加餐来两块小型犬不推荐查看文章精彩评论,请前往什么值得买进行阅读互动

⊙﹏⊙

台积电申请半导体装置及其制造方法及位准移位器电路专利,达成临限...一种位准移位器电路的中电压晶体管可包括衬底中的 p 阱区。此外,中电压晶体管可包括其中包括中电压晶体管的 N+源极/漏极区的 n 型轻掺杂源极/漏极(NLDD)区。NLDD 区中的轻掺杂使得能够减小临限电压(Vt),同时使得能够在 N+源极/漏极区处进行中电压操作。为了减少因 NLDD 区...

∪0∪

˙^˙ 天合光能申请太阳能电池及其制备方法专利,降低PN复合从而进一步...隧穿氧化连接层设置在n+掺杂连接层靠近p+掺杂层的一侧,正面电极与n+掺杂层连接。n+掺杂连接层极易与正面电极形成良好的接触,从而使得两者之间保持较小的接触电阻,隧穿氧化连接层的隧穿能力能够降低p+掺杂层与n+掺杂连接层之间的PN复合,从而在正面电极具有良好接触的基础...

∩▂∩

格力电器申请UMOSFET专利,优化器件的反向恢复性能方法包括:在预处理后的衬底原料的上表面进行离子注入处理得到嵌入衬底原料的P型基区注入区、第一P+注入区和N+注入区;在N型外延层的上表面进行刻蚀处理形成碳化硅沟槽;对碳化硅沟槽进行多晶硅沉积,得到填充碳化硅沟槽的多晶硅栅电极;在第一P+注入区的上表面、N+注入区的...

上海贝岭申请内嵌异质结二极管的MOSFET及其制造方法专利,降低了...N型衬底、N+缓冲层、多层N‑外延层、P型体区、JFET区、P+接触区、N+源区、栅氧化层、N型多晶硅栅极、二氧化硅层间介质、P型多晶硅和金属化源极;JFET区位于两个P型体区的中间;P型多晶硅设于两个N型多晶硅栅极的中间位置,位于JFET区的上方,P型多晶硅与JFET区形成异...

迅达加速器部分文章、数据、图片来自互联网,一切版权均归源网站或源作者所有。

如果侵犯了你的权益请来信告知删除。邮箱:xxxxxxx@qq.com

上一篇:p n是什么意思

下一篇:p n是什么意思中文